#

Artificial Intelligence formulated this projection for compatibility purposes from the original article published at Global Journals. However, this technology is currently in beta. *Therefore, kindly ignore odd layouts, missed formulae, text, tables, or figures.*

# <sup>1</sup> An Efficient Routing Implementation for Irregular Networks

Chand Mal Samota<sup>1</sup>, Naveen Choudhary<sup>2</sup> and Naveen Choudhary<sup>3</sup>

<sup>1</sup> Maharana Pratap University of Agriculture and Technology

Received: 15 December 2013 Accepted: 31 December 2013 Published: 15 January 2014

#### 6 Abstract

7 with the recent advancements in multi-core era, workstation clusters have emerged as a

<sup>8</sup> cost-effective approach to build a network of workstations (NOWs). NOWs connect the small

<sup>9</sup> groups of processors to a network of switching elements that form irregular topologies.

<sup>10</sup> Designing an efficient routing and a deadlock avoidance algorithm for irregular networks is

<sup>11</sup> quite complicated in terms of latency and area of the routing tables, thus impractical for

<sup>12</sup> scalability of On Chip Networks. Many deadlock free routing mechanisms have been proposed

<sup>13</sup> for regular networks, but they cannot be employed in irregular networks. In this paper a new

- 14 methodology has been proposed for efficient routing scheme, called LBDR-UD, which save the 15 average 64.59

- 16

2

3

17 Index terms—up\*/down\*, routing, LBDR, irregular networks, lBDR-UD.

## 18 1 Introduction

ulti Processor-SoC (MPSoC) and Chip-Multi Processors (CMP) achieve high performance with interconnection 19 networks that give lowlatency, high-bandwidth inter-processor communication [7]. Most of these multi-core 20 system use regular topologies (such as torus, hypercube and mesh) to link their switch components. For packet 21 transmission, many routing schemes have been design to provide an efficient and deadlock free path [1,2,4,5,8,10]. 22 23 Routing algorithm (RA) decides the path for the packet from source to destination. Two type of RA i.e. 24 distributed and source routing are used for regular and irregular NoC networks [8]. Source routing compute the whole routing path at the source and computed path stored in the packet header, while in distributed routing 25 each router receives a packet; all computations are performed at the switch level, without storing whole path in 26 27 packet header and decides the output direction to send it. In recent years, several routing schemes have been proposed for application specific networks (i.e. Irregular networks) ??6,9,11,12,13,14,15,16]. 28

29 schemes are able to route packets in different network topologies and achieves livelock and deadlock freedom.

30 To deal with irregular topologies, table based appro-aches were proposed. In this scenario, at each switch that

31 stores a table, for each end-node, the output port that must be used. Using this approach higher adaptivity

32 is achieved and several outputs are stored in each table. The main benefit of this type of routing is that any

33 topology and any routing algorithm can be used; it also supports fault-tolerant routing algorithms. With such

34 routing approaches, the size of routing table increases proportionally with the size of the network at each switch.

35 Hence, the implementation becomes comparatively complex for the communication switch.

In this paper a efficient routing algorithm is proposed for irregular networks. The aim is to develop a distributed routing on every switch and remove the tables, the routing decision is made quickly and low latency for packets sending from source to destination. The wormhole switching technique is used in our interconnection networks. The routing algorithm is based on combination of up\*/down\* and LBDR, and hence called LBDR Up\*/Down\* (LBDR-UD). [12] up\*/down\* routing is distributive table-based routing algorithm used in the irregular network and [7] LBDR is a table-less routing implementation technique for regular and irregular networks (generated from

42 the mesh).

#### 43 **2** II.

## 44 3 Lbdr-ud Routing for Irregular Networks

45 We start the description with the basic mechanism required at every switch to deal with the irregular networks.

#### $_{46}$ 4 a) Methodology

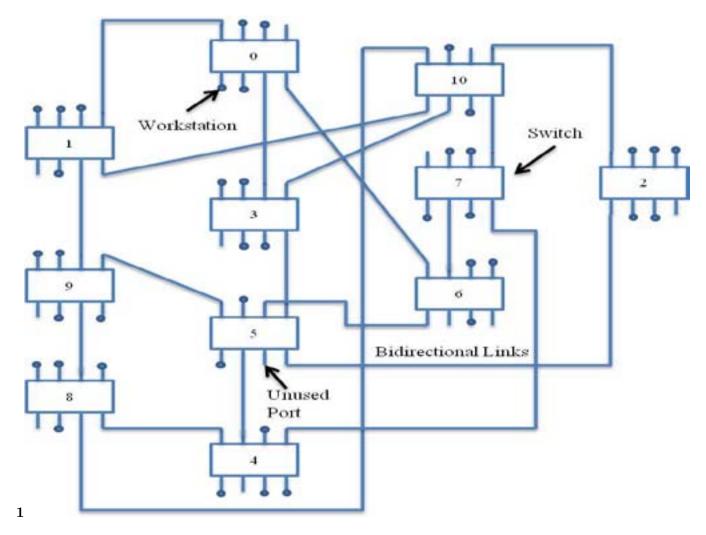

In order to enable an efficient routing implementation for irregular networks using minimum logic, an example

network for irregular Network-on-Chip with core and channels are placed according to the application condition

as shown in Fig. 1.

50 The proposed methodology is based on two assumptions:

51

i.

The interconnection network between switches can be modeled by a multigraph G (N, C), where N is the group of switches and C is the group of bidirectional links between the switches. These ii. For each irregular networks, applied routing algorithm must follow some restrictions. These restrictions are as follows: a. Deadlock-freedom The routing algorithm must guarantee that the transmitted messages are received at destination and prevent

56 the deadlock scenarios.

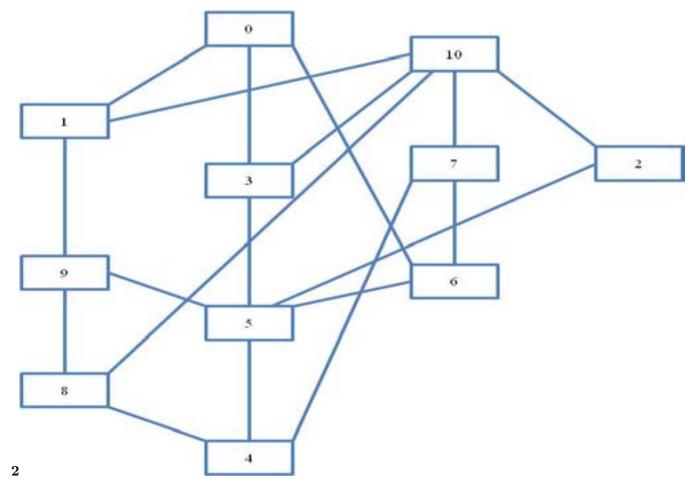

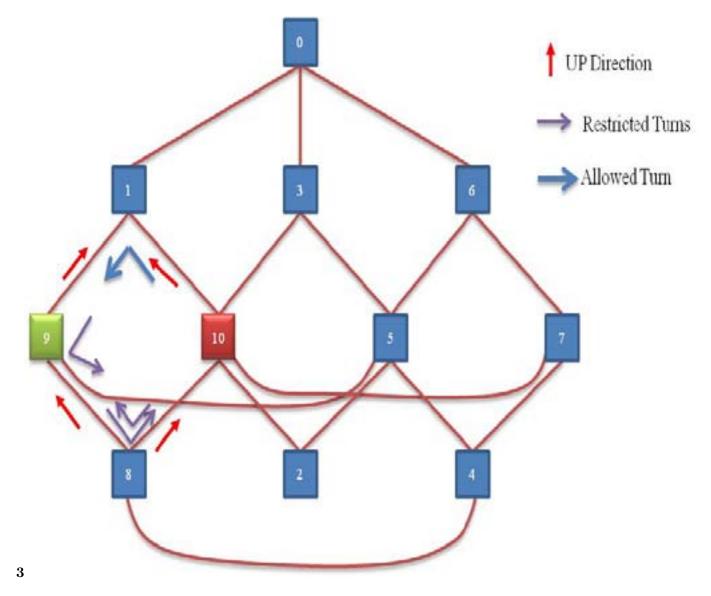

b. Connectivity It is essential that the routing algorithm should be capable to offer at least one route between 57 two end nodes. Routing is based on a direction assignment to the operational links, including the ones that 58 do not belong to the tree. In particular, the "up" direction of each link is defined as: 1) A link leading to a 59 parent node in the spanning tree; 2) A link leading to a lower ID, if both are at the same tree level. The "down" 60 direction is along the reverse direction of the "up" direction as shown in Fig. 2. The routing restrictions for 61 the LBDR-UD routing algorithm are shown in Fig. 2. A routing restriction is defined between two successive 62 channels. The LBDR-UD algorithm prohibits messages from taking "downup" transitions. The transitions are 63 allowed in opposite direction by algorithm, thus routing restrictions does not exist for "up" link to "up" and 64 "down" links. Similarly, no routing restrictions are applicable from "down" link to "down" link transitions. 65

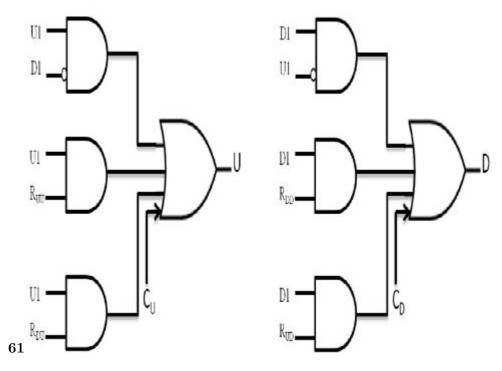

### <sup>66</sup> 5 b) Configuration bits

Configuration bits are in two sets: connectivity bits and routing bits. Routing bits specify which routing options

can be used, whereas connectivity bits specify connectivity with neighbors.

#### 69 6 R UU and R UD

These bits indicate that the message can take the "up" direction from the current router and from the next router the message can be transmitted in the "up" direction or the "down" direction respectively.

## <sup>72</sup> 7 R DD and R DU

73 These bits indicate that the messages can take the "down" direction from the current router and from the next 74 router the message can be transmitted in the "down" direction or the "up" direction respectively.

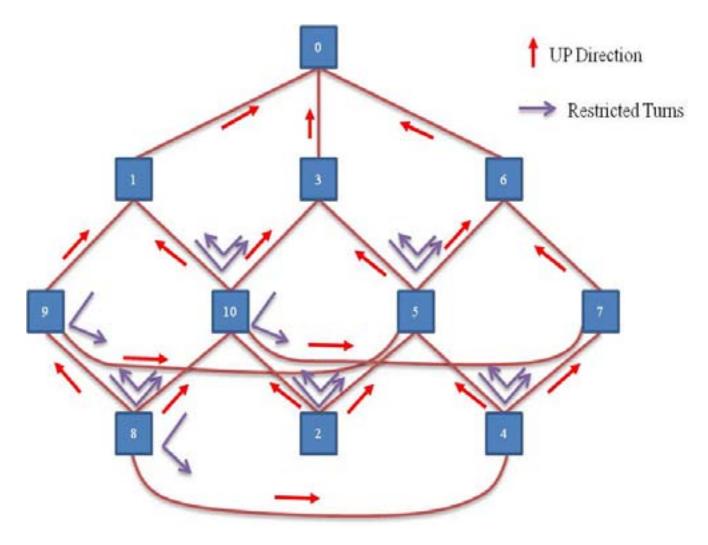

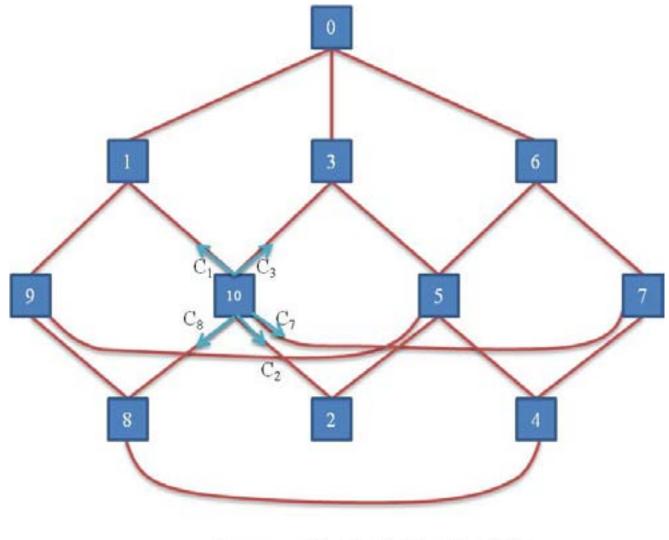

Note that the routing restrictions and routing bits are the opposite to each other. Fig 3(a) shows the restricted 75 turns and allowed turns a message could take according to router 10 and its routing bits. Specifically, bit RUD at 76 router 10 is 1(Set) and shows that a message is routed to the "up" direction first and then to the "down" direction 77 from the next router. Routing decision is taken again at the next corresponding router. Table ?? shows the 78 bits computed for an irregular network using the LBDR-UD routing algorithm (connectivity bits can be seen in 79 80 Fig. 3(b)). As shown in the figure, bit R DU is set to zero, representing the "down" to "up" routing restrictions 81 which "LBDR-UD" imposes. Bits R UU and R DD are all set except for those cases where the message would be routed out of the network (at the root router and leaf router). R UD is set ("up" to "down" transitions are 82 allowed) except for those cases where the message would be routed out of the network. 83

Finally, based on neighboring routers, connectivity bits are set.

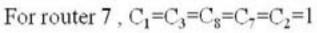

Fig. 4 shows the algorithm in pseudo-code for the computation of configuration bits. Function check link 85 shows that whether a link between current router and neighboring router exist or not. Based on the type of 86 restriction the routing bit is set on behalf of its immediate neighbor router. In the LBDR-UD routing only single 87 turn (RDU) is restricted and rest three turns (RUU, RDD and RUD) are allowed. The propose algorithm is 88 flexible, simple and compact routing mechanism for unicast communication that eliminates the requirement for 89 routing tables at every router. The routing logic is separated in two stages. The first stage computes the location 90 91 of the relative destination router. A general representation of LBDR-UD routing is shown in Fig. 5 and Fig. 92 ?? Initially a comparator module is used, which generates two control signals using three comparators. First 93 comparator (CMP) is used to compare the current\_id\_level and Dest\_id\_level, and if the levels are equal then it compares using the Direct Connection CMP otherwise the Ancestor CMP is used. These signals, U1 and D1 94 indicate the relative direction of the destination in "up" direction and "down" direction respectively. 95

For example, in Fig. 2, if the current router is 7 and our destination is router 6, signal U1 would be set, because it is situated at the lower level in comparison with the current router. With the help of these connectivity (C U) bits, routing (R UD) bits and control signals, the LBDR-UD routing generates a set of routing Table ?? Connectivity bits for an irregular network, Routers are numbered row-wise. (See Fig. 3(b)) The second stage

When any of the falling out three conditions is fulfilled, then the incoming packet is headed in "up" output direction for routing. The "up" direction is not considered for routing the packet when none of the following conditions are fulfilled (additionally, the connectivity bit CU is examine in order to filter the up direction).

109  $\,$  ? The destination is directly connected with destination 1 1 D U  $\times$

? The destination is the ancestor of source router and the message can take the up direction at the lower level router through the up direction output port UU R U  $\times$  1

112

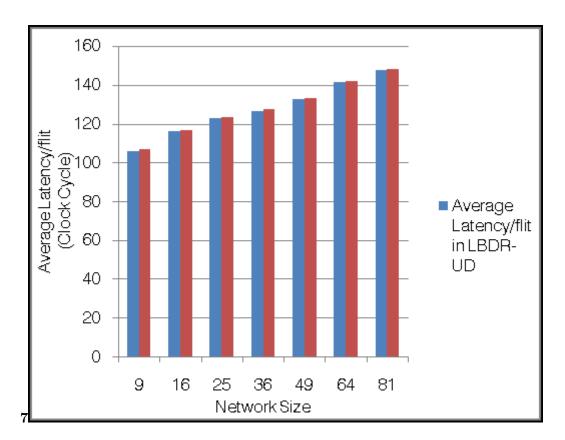

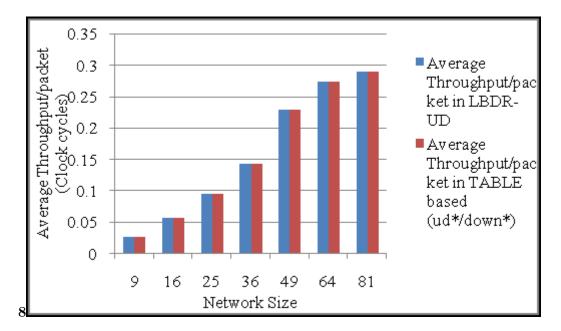

### 113 8 Results and Analysis

In the following, we provide performance evaluation of LBDR-UD and TABLE based (up\*/down\*) with different

network size. Average memory, latency and throughput are calculated on 10 different scenario of each network

size (Total 60 scenarios).

## <sup>117</sup> 9 a) Effect of Network Size on Memory

Distributed Table based routing schemes have also been proposed to deal with irregular topologies and can be used in application-specific systems which facilitates the use of any topology with any routing algorithm. On small systems the hardware cost and power consumption related to the memories used to build routing tables is affordable, but as more and more cores are integrated on the chip, causing the system

## 122 **10** Conclusion

It is extension of up\*/down\* routing in irregular networks using LBDR. LBDR-UD minimizes the memory space of the table based routing (up\*/down\*) in the NoC for irregular networks. On the behalf of simulation evaluation LBDR-UD save the average 64.59% tables and also efficient in terms of network average latency/flit and throughput/packet as compare to TABLE based (up\*/down\*) routing.

<sup>127</sup> In application specific topologies (Irregular networks) LBDR also used for 3D irregular networks and this research will be extended by designing the efficient router architecture for NoC. Year 2014

Figure 1: M

Figure 2: Figure 1 :

128

$<sup>^1 \</sup>odot$  2014 Global Journals Inc. (US)

Figure 3: Figure 2 :

Figure 4: An

Figure 5: Figure 3 :

$\mathbf{4}$

Figure 6: Figure 4 :

*Input* : Topology definition with location of routing restriction and existent links *Output* : Configurat ion bits

Procedure :

//checking connectivi ty bits of current router for each router

for(all neighbours of current router)

Cn = 1; //connect ivity bit of neighbour

end for

*for each* router *//*checking restriction, defined as unidirectional getRouting Restriction(Curr\_id); *end for*

Figure 7: An

Figure 8: Figure 5 :

Figure 9: Figure 6 :× 1 .

Figure 10: Figure 7 :

Figure 11: Figure 8 :

Figure 12:

#### <sup>129</sup> .1 Global Journals Inc. (US) Guidelines Handbook 2014

- 130 www.GlobalJournals.org

- 131 [Boppana and Chalasani ()] 'A Comparison of Adaptive Wormhole Routing Algorithms'. R V Boppana , S

Chalasani . Proceeding Intel Symposium on Computer Architecture, (eeding Intel Symposium on Computer

Architecture) 1993. p. .

- [Sancho et al. ()] 'A new methodology to compute deadlock free routing tables for irregular networks'. J C Sancho

A Robles , J Duato . *Proceedings of the CANPC*, (the CANPC) 2001.

- [Duato ()] 'A New Theory of Deadlock-Free Adaptive Routing in Wormhole Networks'. J Duato . IEEE Trans.

On Parallel and Distributed Systems 1993. 4 (12) .

- [Sun et al. ()] 'An efficient deadlock-free tree-based routing algorithm for irregular wormhole-routed networks

based on turn model'. Y M Sun , C H Yang , Y Chung , T Y Hang . International Conference on Parallel

*Processing*, 2004. 1 p. .

- 141 [Schroeder et al. ()] 'Autonet: A highspeed self-configuring local area network using point-to-point links'. M D

- Schroeder, A D Birrell, M Burrows, H Murray, R M Needham, T L Rodeheffer, E H Satterthwaite, C

P Thacker. Journal on Selected Areas in Communications 1991. 9.

- [Dally and Seitz ()] 'Deadlock-Free Message Routing in Multiprocessor Interconnection Networks'. W J Dally ,

C L Seitz . *IEEE Trans. on Computers* 1987. 36 (5) p. .

- [Wu and Sheng ()] 'Deadlock-free routing in irregular networks using prefix routing'. J Wu , L Sheng . DIMACS

*Tech. Rep* 1999. p. .

- 148 [Silla et al. ()] 'Efficient adaptive routing in networks of workstations with irregular topology'. F Silla , M P

- Malumbres, A Robles, P Lopez, J Duato. Proceedings of the Workshop on Communications and Architectural

Support for Network-Based Parallel Computing, (the Workshop on Communications and Architectural

Support for Network-Based Parallel Computing) 1997. p. .

- 51 Support for Network-Dased Faraner Computing) 1997. p. .

- [Silla and Duato ()] 'High-performance routing in networks of workstations with irregular topology'. F Silla ,

Duato . *IEEE Transactions on Parallel and Distributed Systems* 2000. 11 p. .

- IJouraku et al. ()] 'L-turn routing: an adaptive routing in irregular networks'. A Jouraku , A Funahashi , H

Amano , M Koibuchi . International Conference on Parallel Processing, 2001. p. .

- [Flich and Duato ()] 'Logic based distributed routing for NOCs'. J Flich , J Duato . *IEEE computer architecture letters* 2008. 7 (1) .

- [Ni and Mckinley ()] L M Ni , P K Mckinley . A Survey of Wormhole Routing Techniques in Direct IEEE on

Computers, 1993. 26 p. .

- [Chien and Kim ()] 'Planar-Adaptive Routing: Low-Cost Adaptive Networks for Multiprocessors'. A Chien , J

H Kim . Journal of ACM 1995. p. .

- 162 [Choudhary ()] Principles of on-chip Interconnection Networks, N Choudhary . 2013. Himanshu Publication.

- [Glass and Ni ()] 'The Turn Model for Adaptive Routing'. C J Glass , L M Ni . Proceeding Intel. Symposium on

Computer Architecture, (eeding Intel. Symposium on Computer Architecture) 1992. p. .