# Global Journals $end{transformula} \mathbb{A}T_{\mathbf{E}} X$ JournalKaleidoscope

Artificial Intelligence formulated this projection for compatibility purposes from the original article published at Global Journals. However, this technology is currently in beta. *Therefore, kindly ignore odd layouts, missed formulae, text, tables, or figures.*

| 1<br>2 | Reduction of Power Consumption using Different Coding<br>Schemes using FPGA in NoC |

|--------|------------------------------------------------------------------------------------|

| 3      | Mitkari Sneha U. <sup>1</sup> and Prof. Dr. S. S. $Chorage^2$                      |

| 4      | $^1$ Bharati vidya<br>peeth's college of engineering for Women, Katraj,Pune-43.    |

| 5      | Received: 9 December 2016 Accepted: 31 December 2016 Published: 15 January 2017    |

#### 7 Abstract

Network-On-Chip (NoC) is used as a main part of a system. NoC overcomes traditional System-On-Chip (SoC) problems. Because, SoC has problems like cost, design risk, more 9 complexity and more power consumption. In software part, Xilinx ISE Design suite 14.5 with 10 VHDL programming is used. It is simple programming language. In hardware part, FPGA of 11 Spartan 3E family is used. It is advanced 90nm technology. It is world?s the cheapest FPGA 12 family. It has 500K gates and 40 LUTs. It has lowest cost per logic. Its better advantage is 13 that it is designed for more volume-to-market. Power consumption of given system is 14 compared with previous system. From output power analysis chart, it is concluded that given 15 system has lower power consumption than previous system. Power consumption of gray to 16 binary conversion block of previous system is nearly equal to power consumption of present 17 (given) whole system. This proves that there is a great reduction in power consumption in the 18 system. 19

20

21 Index terms— FPGA, LUTs, Network-on-Chip (NoC), System-on-Chip (SoC), Spartan 3E, VHDL.

#### <sup>22</sup> 1 I. Introduction

Design density and total length of interconnection wires are directly proportional with each other. This affects on long distant transmission delay and higher power consumption.

# <sup>25</sup> 2 II. Related Work

<sup>26</sup> Giuseppe Ascia, et al. [1],

In this paper, we propose the data encoding techniques are used to reduce both power dissipation and energy consumption of NoC links Working on the basis of end-to-end, the proposed encoding scheme exploits the wormhole switching techniques.

That is, encoding and decoding of flits by NIs at source and destination. Shivaraj MN, et al. [2], Jeeva Anusha, et al. [3],

In the proposed system, different encoding schemes are given. Also, hardware design properties are presented.

33 Output details and power details are given.

## <sup>34</sup> 3 III. Proposed System

In method 1, Encoding is done by reducing number of type-I, II transitions and converting them to type-III and / or Type IV transition. Network-on-Chip power dissipation sources (links) [1] s process technology scaling continues number of transistor increases and hence power consumption also increases. Chip-multiprocessor can reach higher efficiency due to synchronized parallel execution of multiple programs or threads. Network-on-Chip is a scalable alternative to conventional when core count is more in Chip-multiprocessor. For mainly in current VLSI design, power efficiency is very important constraint in NoC design. In this paper, encoding techniques are used to reduce dynamic power reduction than previous system. Coupling switching activities are reduced.

Detailed process of inversion is explained with the help of flowchart.

Author ? ?: Electronics and telecommunication, Department Bharati Vidyapeeth's College of Engineering for Women Pune, 43 , Savitribai Phule Pune University, Maharashtra, India. e-mails: suvarna.chorage@bharatividyapeeth.edu, snehamitkari@gmail.com Here, capacitance is in µF. So, it is very negligible.

47 () (3)**2**

48 From (2) and (4),

49 From (2) and (??),

50 We know energy formula with respect to voltage and capacitance.

These two formulae are the basic formulae for energy and power. ? As shown in Table **??2**, number of logics increases efficiency. As number of signals decreases power consumption also decreases from scheme-1to scheme-3. ? In previous system, for only one stage, i.e. Gray Encoding block, dynamic power consumption was 0.3mW.And now, in the present system after summing for all stages, dynamic power consumption is 0.46mW.From this comparison is done. We can conclude that power consumption is minimized in more amounts.W = (1/2)(???? 2) P = W/t W = VIt W/t = VIt /t = VI P = VI W/t = (1/2)(???? 2)/t 1/2 (???? 2)f = P P = (1/2)(??????

57 2)

#### <sup>58</sup> 4 VI. Results and Discussion

a) Scheme-I In scheme-I, half invert and full invert is performed. In full invert, 00 is converted into 11. When

any one of the two is performed then inversion bit is set to 1, otherwise it is set to 0.

## <sup>61</sup> 5 b) Scheme-II

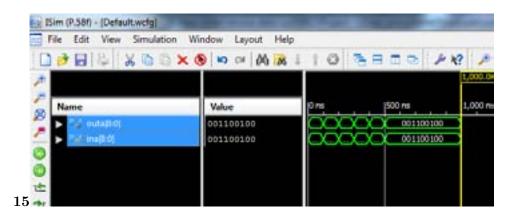

62 Simulation is done on Xilinx 14.5 ISE simulator. It is backend design tool. In scheme-II odd inversion is added.

63 Type-II transitions are converted into type-IV transitions. Data coming at Network interface is from Encoder

<sup>64</sup> block. Then it is converted into desired encoded data which is passed through number of routers. This type of <sup>65</sup> encoding is of scheme-II.

# 66 6 c) Scheme-III

In scheme-III, there is additional inversion is performed that is Even inversion. For that Te block is added in

second stage. Here, power consumption will be less than Scheme-II because; link power consumption is minimized

in more amounts.

70 Binary bit has some switching problem. So, they are converted into gray bits.

# 71 7 d) Results obtained by LCD Interfacing

To calculate report for power consumption, first, we have to interface encoder and decoder with LCD. On this LCD, we can see desired output for both stages, encoding and decoding.

Here, 'en' is for enable, 'clk' is for clock and 'rs' is for register select. When there is initialization of lcd rs=0.

$^{75}$  When rs=1, data is as it is written on lcd. When en=1, module is enabled or is started.

## 76 8 VII. Conclusion

? Encoding and decoding operation is used for security purpose. But here, main aim is to reduce power

consumption in a effective way. ? Hardware part is used in such a way that cost of Spartan 3E (for Xilinx) is

the lowest among different FPGA families. ? Dynamic power consumption without interfacing is calculated and

$\infty$  compared with previous systems. ? In scheme-I, II, III, on the basis of parameters, power analysis is done.

#### 81 **9** A

82 Reduction of Power Consumption using Different Coding Schemes using FPGA in NoC 1 2

$<sup>^{1}(</sup>$ )@2017 Global Journals Inc. (US) 1

$<sup>^{2}</sup>$ © 2017 Global Journals Inc. (US)

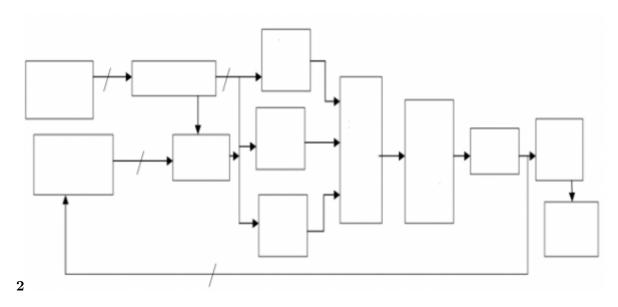

Figure 1: Fig. 2 :

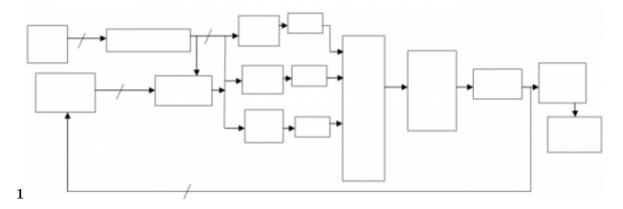

Figure 3: Fig. 1 :

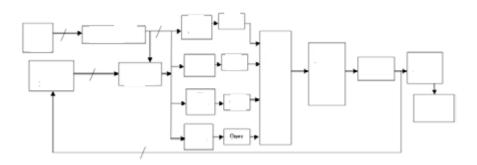

Figure 5: Fig. 5 :

| Name:                                  | main                              |                               |

|----------------------------------------|-----------------------------------|-------------------------------|

| Location:                              | ErWew folder (enova data cust (ME | 2Project-Jacheme 3main - Icd  |

|                                        |                                   |                               |

| Working directory:                     | E: Wew folder Venova data cust WE | staudiechAbcueuse sunau - ich |

| Description:                           |                                   |                               |

| Project Settings                       | here.                             |                               |

| Property Name                          | Value                             |                               |

| Top-Level Source Type                  | HDL                               |                               |

| Evaluation Development Board           | None Specified                    |                               |

| Product Category                       | All                               |                               |

| Family                                 | Spartan3E                         |                               |

| Device                                 | XC3S500E                          |                               |

| Package                                | PQ208                             |                               |

| Speed                                  | -5                                |                               |

| Synthesis Tool                         | XST (VHDL/Verilog)                |                               |

| Simulator                              | ISim (VHDL/Verilog)               |                               |

| Preferred Language                     | VHDL                              |                               |

| Property Specification in Project File | Store all values                  |                               |

| Manual Compile Order                   | <b>m</b>                          |                               |

| VHDL Source Analysis Standard          | VHDL-93                           |                               |

| Enable Message Filtering               | (m)                               |                               |

Figure 6: Fig. 6 :

| On-Chip                                                                                                 | Power                                   | r (m₩) | I U | Üsed | I A | vailable | I | Utilization | (*) |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------|--------|-----|------|-----|----------|---|-------------|-----|

| Clocks                                                                                                  | I                                       | 0.46   | 1   | 1    | 1   |          | 1 |             |     |

| Logic                                                                                                   | 1                                       | 0.00   | 1   | 144  | 1   | 5720     | 1 |             | 3   |

| Signals                                                                                                 | 1                                       | 0.00   | 1   | 175  | 1   |          | 1 |             |     |

| IOs                                                                                                     | 1                                       | 0.00   | 1   | 20   | 1   | 102      | 1 |             | 20  |

| Static Power                                                                                            | 1                                       | 13.69  | 1   |      | 1   |          | 1 |             |     |

| Total                                                                                                   | 1                                       | 14.15  | 1   |      | 1   |          | 1 |             |     |

| 2.2. Thermal Summary                                                                                    | 7 I                                     |        |     |      |     |          |   |             |     |

|                                                                                                         | <br>7 I                                 |        |     |      |     |          |   |             |     |

|                                                                                                         |                                         |        |     |      |     |          |   |             |     |

| Thermal Summary<br>  Effective TJA (C/W)<br>  Max Ambient (C)                                           | 38.4  <br>  84.5                        |        |     |      |     |          |   |             |     |

| Thermal Summary                                                                                         | 38.4  <br>  84.5                        |        |     |      |     |          |   |             |     |

| Thermal Summary<br>  Effective TJA (C/W)<br>  Max Ambient (C)<br>  Junction Temp (C)                    | 38.4  <br>  84.5  <br>  25.5            |        |     |      |     |          |   |             |     |

| Thermal Summary<br>  Effective TJA (C/W)<br>  Max Ambient (C)                                           | 38.4  <br>  84.5  <br>  25.5            |        |     |      |     |          |   |             |     |

| Thermal Summary<br>Effective TJA (C/W)<br>Max Ambient (C)<br>Junction Temp (C)<br>2.3. Power Supply Sur | 38.4  <br>  84.5  <br>  25.5  <br>nmary |        |     |      |     |          |   |             |     |

| Thermal Summary<br>Effective TJA (C/W)<br>Max Ambient (C)<br>Junction Temp (C)<br>2.3. Power Supply Sur | 38.4  <br>  84.5  <br>  25.5            | Summar | у   |      |     |          |   |             |     |

| -    |        |  |  |  |       |  |  |  |       | <br> |

|------|--------|--|--|--|-------|--|--|--|-------|------|

|      | Supply |  |  |  | 14.15 |  |  |  | 13.69 | 1    |

| 344- | 344    |  |  |  |       |  |  |  |       |      |

Figure 7: Fig. 3 : Fig. 4 : Fig. 4 :

| 0        |        |           |                        |                             |     |

|----------|--------|-----------|------------------------|-----------------------------|-----|

|          |        | ********* |                        |                             |     |

| Generat  |        |           |                        | (R) RTL Compiler v09.18-p10 | 4_1 |

| Generat  |        | -         |                        | 14 12:37:49 PM              |     |

| Module:  |        |           | Encoder                |                             |     |

|          |        |           | tsmc18 1.0             |                             |     |

| Wireloa  | -      |           | slow (bala<br>enclosed | inced_tree)                 |     |

| Area mo  |        | e.        |                        | 1000                        |     |

| Area no  | ue:    |           | timing li              | nary                        |     |

|          |        |           |                        |                             |     |

|          |        | Leakage   | Dynamic                | Total                       |     |

| Instance | Cells  | Power(nW) | Power(nW)              | Power(nW)                   |     |

| Encoder  | 102    | 88.551    | 332047.860             | 332136.411                  |     |

| cal1     | θ      | 0.000     | 24472.530              | 24472.530                   |     |

| cal2     | 0      | 0.000     | 24472.530              | 24472.530                   |     |

| cal3     | Θ      | 0.000     | 24472.530              | 24472.530                   |     |

| cal4     | 8<br>8 | 0.000     | 24472.530              | 24472.530                   |     |

| r1       | Θ      | 0.000     | 322.801                | 322.801                     |     |

| r2       | 0      | 0.000     | 367.416                | 367.416                     |     |

| 14       | 0      | 0.000     | 713.837                | 713.837                     |     |

| r3       |        | 0.000     | 320.177                | 320,177                     |     |

Figure 8: A 4 ] Fig. 7 : Fig. 8 : Fig. 9 : Fig. 10 :

| and the second | ndew Layout Help | a substance of the | in the |

|------------------------------------------------------------------------------------------------------------------|------------------|--------------------|--------|

| ) 🦻 🖬 🛝 🛛 🛣 🖬 📉 🗙 🐧                                                                                              | e ⊨o c≃ 245 26 ⊥ | IO GEOG A          | B10000 |

| Name                                                                                                             | Value            | 0 ns  500 ns       | 1,000  |

| <ul> <li>Tot estation</li> <li>Tot estation</li> </ul>                                                           | 101110100        |                    |        |

|                                                                                                                  |                  |                    |        |

|                                                                                                                  |                  |                    |        |

Figure 9: Fig. 12 :

Figure 10: Fig. 15 :

| the state of the second s | indow Layout Help |       |        |            |     |       |          |       |       |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|--------|------------|-----|-------|----------|-------|-------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8 M M M M         | TO    | - B    |            | 140 | PP    | 81       | 3 ± ± | 11031 | 20 × |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |       |        |            |     |       |          |       |       | 1,00 |

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Value             | D res |        | 1200 mil   |     | 00 m  | 1600     | -     | 800 m | 1.00 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EC.               | 00    | X 01   | Provide la |     | THE P |          | TIMM  |       | 1.0  |

| 5220-Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 01                | 01    | X 00   | Ŷ          |     |       | 00       |       |       |      |

| p.000 📂 🔰 📢                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 01                | 100   | x      | 1          |     |       | 61       |       |       |      |

| 🔿 🕨 💐 inpresent[8:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 000001010         | 00101 | 10031  | X. —       |     |       | 00000901 | 0     |       |      |

| 🛧 🕨 💐 inprevisus(80)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 001000110         | 00001 | 00001  | x —        |     |       | 00330033 | 0     |       |      |

| 12 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |       | Access | <u>^</u>   |     |       |          | ž     |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |       |        |            |     |       |          |       |       |      |

Figure 11: Fig. 17 :

# $\mathbf{2}$

| Parameter     | Scheme-1            | Scheme-2           | Scheme-3           |

|---------------|---------------------|--------------------|--------------------|

| Family        | Spartan-3E          | Spartan-3E         | Spartan-3E         |

| Device        | XC3S500E XC3S500E X | C3S500E            |                    |

| Package       | PQ208               | PQ208              | PQ208              |

| Speed         | 5                   | 5                  | 5                  |

| Clock         | 1                   | 1                  | 1                  |

| Logics        | 148                 | 163                | 144                |

| Signals       | 197                 | 177                | 175                |

| IOs           | 20                  | 11                 | 20                 |

| Dynamic Power | $0.46\mathrm{mW}$   | $0.46\mathrm{mW}$  | $0.46\mathrm{mW}$  |

| Static Power  | $13.69\mathrm{mW}$  | $13.69\mathrm{mW}$ | $13.69\mathrm{mW}$ |

Figure 12: Table 2 :

- [Jeeva Anusha et al. (2015)] 'Article 06596'. V Jeeva Anusha , "Thrimurthulu , Vlsi , Of , Low , Modeling ,

Network , Chip . International Journal of VLSI and Embedded Systems (IJVES), June 2015. 06.

- <sup>85</sup> [Dannana et al. ()] 'Data Driven Data Encoding for Low Power Application'. Suresh Dannana , Govinda Rao

<sup>86</sup> Tamminaina , A R V Kumar . *Image Processing and Pattern Recognition(IPPR)*, 2015. 8 p. .

- [Jafarzadeh et al. (2014)] 'Data Encoding Schemes for Reducing Energy Consumption in NoC'. Nima Jafarzadeh

, Maurizio Palesi , Ahmed Khademzadeh , Ali Afzali-Kusha . *IEEE transaction on VLSI system*, march 2014.

22.

- [Ascia and Catania (2016)] 'Data Encoding Schemes in Networks on Chip'. Maurizio Ascia, Fabrizio Fazzinoand

Vincenzo Catania. *IEEE transaction on computer aided design of integrated circuits and systems* may 2016.

30 (5).

- [Anisha and Sarathbabu (2014)] 'Data Encoding Techniques for Lower Power Dissipation in NoC'. D Anisha, R

Sarathbabu . International Journal of Engineering Research & Technology( IJERT) February -2014. 3.

- <sup>95</sup> [Soujanya et al. ()] 'Data Encoding Techniques for Reducing Energy Consumption in Network-on-Chip'. Akula

<sup>96</sup> Soujanya, . P Mrs , Vinitha, . K Mr , Gopi . International Journal of Eminent Engineering Technologies

<sup>97</sup> NOV 2015. 4 (2) .

- 98 [Shivaraj et al. (2015)] 'Dynamic Power Reduction in NOC by Encoding Techniques'. M N Shivaraj , H Ravi ,

- Talawar . IJIRST (International Journal for Innovative Research in Science & Technology) September 2015.

2 (04) .

- [Chetan et al. (2014)] 'ENCODING SCHEMES FOR POWER REDUCTION IN NETWORK ON CHIP

LINKS'. S Chetan , Behere , Somulu , Gugulothu . International Journal of Research in Engineering and

- 103 Applied Sciences July 2014. 02 p. 2. (IJREAS))

- 104 [Giuseppe Ascia, Fabrizio Fazzino and Vincenzo Catania Data Encoding Schemes in Networks on Chip by Maurizio Palesi (2016)

- 'Giuseppe Ascia, Fabrizio Fazzino and Vincenzo Catania'. Data Encoding Schemes in Networks on Chip by

Maurizio Palesi, may 2016. 30.

- 107 [Manoj et al. (2014)] 'Power Consumption in Networkon-Chip by Encoding Scheme'. A V Manoj, S Bhavya Sree

- , K Kumar , V Purandhar Reddy . International Journal of Innovative Research & Development (IJIRD)

January. 2014. 3.