1. Introduction

uilt in self test (BIST) design technique is a part of circuit which is used to test the circuit itself. Engineers design BISTs to satisfy demands such as lower repair cycle times or constraints such as limited technician accessibility and cost of testing during manufacture and high reliability. The main purpose of BIST is to reduce the test complexity, and thereby decrease the cost and reduce dependence upon external (pattern programmed) test equipment [1]. Built in self test techniques are very useful in testing of logic circuits, because they offer a cost effective way to test complex digital devices. First the BIST concept was implemented on combinational circuits, after that it found quick demands in the testing of regular structures like programmable logic arrays, read only memories, and random access memories.

Quick increment of multifaceted nature in the integrated circuits has prompt impact following on memory testing. On one view, the limit of randomaccess memories upgrades, in this manner expanding the test time and cost, on the other view, the complexity of memory circuits becomes more, and therefore more failure modes and faults should be considered in order to get a product with good quality [4]. Accordingly, different constraints need to take care while considering a test algorithm.

Minimizing the number of memory operations in order to allow large capacity memories to be tested in proper period of time and covering a larger collection of memory faults. In the last previous days of memory design test procedures were developed in an ad-hoc manner. The fault coverage of these ad-hoc test procedures was limited and often indeterminable [2]. This shortcoming, acknowledged by most researchers, motivated the introduction of such fault models as stuck-at faults, decoder faults, coupling faults. If density of memory circuits increases, it increases coupling effects then the pattern sensitive fault PSF is becoming very important fault model [3].

The

2. b) Neighborhoods Pattern Sensitive Faults

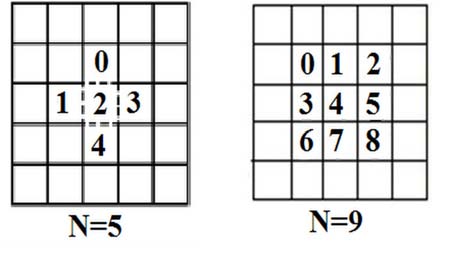

A Pattern Sensitive Fault is a restrictive coupling fault in which the content of a memory cell, or the capacity to change its content, is affected by a specific bit pattern in different cells in the memory. Here the information maintenance and change of the victim cell are influenced by an arrangement of aggressor cells. A neighborhood pattern sensitive Fault (NPSF) is a special instance of pattern sensitive faults [8], wherein the affecting (coupling) cells are in the neighborhood of the impacted (coupled) cell. The coupled cell is known as the base (or victim) cell and the coupling cells are known as the deleted neighborhood cells. The neighborhood incorporates 4 deleted neighborhoods and one base cell. It forms the coupling of these 4 cells with the base cell considering effect as the NPSF fault modeling.

3. c) Active NPSF

The base cell changes its contents because of changes in the deleted neighborhood pattern. To identify these affect, every cell must be read in state 0 and in state 1 for every single conceivable change in the deleted neighborhood pattern. There are two distinctive conceivable states for the base cell (0 and 1), N-1 methods for picking the deleted neighborhood cell which must experience one of two conceivable advances (? or â??"), and N-2 potential outcomes for the rest of the neighborhood cell contents.

2* (N-1)*2*2N-2 = (N-1)* 2N is the aggregate number [8] of active neighborhood patterns (ANPs). It require 128 patterns for identifying active NPSF faults. For type-1 NPSF, 2 is base cell and 0, 1, 3 and 4 are deleted neighborhood cells.

4. d) Passive NPSF

The content of the base cell can't be changed because of a specific neighborhood pattern. Every cell must be written and read in state 0 and in state 1 for all changes of the deleted neighborhood pattern. For each of the 2N-1 deleted neighborhood patterns, the two conceivable advances ? and â??" must be confirmed. Subsequently, the aggregate number of PNPSFs is 2*2N-1=2N. Here N is number of cells. It require 32 test patterns for recognizing active NPSF faults.

5. e) Static NPSF

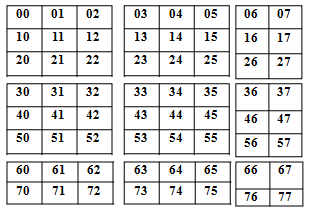

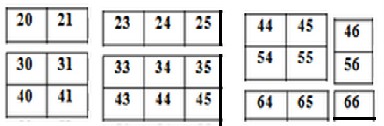

The content of a base cell is compelled to a specific state because of a specific neighborhood pattern. To distinguish these faults, apply the 2N combinations of 0s and 1s to the N-cell neighborhood, and check by perusing every cell that each pattern can be stored. It varies from ANPSF that it is not necessary to have a change to transition to sensitize an SNPSF. We required 32 test patterns for recognizing static NPSF faults. Fig 5 shows that the memory is divided into nine different blocks. Nine test cases are used for testing the memory since maximum size of the block is 9. For test case 1 each block of first cell is selected as base cell then the base cells are selected as 00, 03, 06, 30, 33, 36, 60, 63, 66 and the pattern are applied to the deleted neighborhood cells of each base cell. For test case 2 each block of second cell is selected as base cell then the base cells are selected 01, 04, 07, 31, 34, 37, 61, 64, and 67. Likewise for test case 9 the base cells are selected as 22, 25, 52 and 55.

6. III.

7. Memory Testing

8. Fig. 5: 8*8 memory divides into blocks

If base cell positions are not available in blocks then the base cells are chosen based on their availability [10]. Table 1 shows the base cells according to their respective test case.

9. c) Memory testing by using different test cases

10. d) Algorithm

Step 1: Write all base cells to 1.

Step 2: Applying pattern to neighborhood cells

11. e) Operation

During the 1st operation, cell 1 of each block will be selected as a base cell and the corresponding

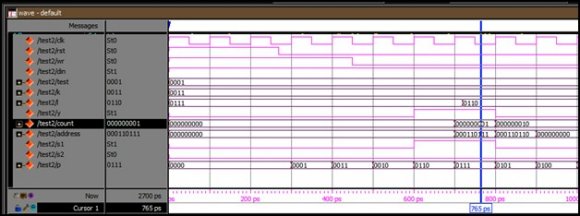

12. b) Xilinx Reports

Xilinx ISE is a software tool is used for synthesis and analysis of HDL designs [11]. Allows the developer to synthesize the design, gives timing analysis, RTL diagrams, and configure the target device with a programming kit. The table 2 shows the summary of device utilization for Nexys 4 DDR Artx 7 FPGA. The utilization of device gives the information of number of LUTs, logic blocks and number of bonded IOBS used in FPGA, it can be obtained from synthesis report generated by Xlinx ISE.

V.

13. Conclusion and Future Scope

For memory arrays, the excessive test algorithmic time associated with NPSF fault model. This paper presents a BIST implementation using block code technique to select base cells and deleted neighborhood cells of neighborhood pattern sensitive faults (NPSFs) in random access memories (RAMs). Testing process is synthesized and implemented on Nexys 4 DDR Artix 7 FPGA board. In order to improve the effectiveness of coupling faults, type-2 NPSFs can be modelled and tested.

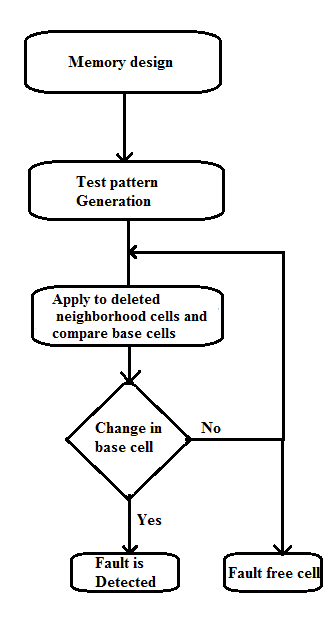

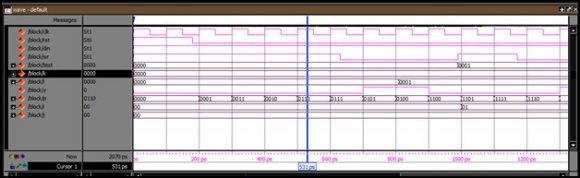

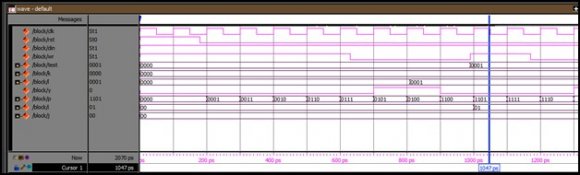

![Fig. 3: Block diagram of memory testing Fig 3 shows the testing process[12]. The pattern generator block generates the patterns for memory testing. These patterns are given as inputs to the deleted neighborhood cells of the selected base cell which are selected by the test controller. Then using the comparator we can find out the base cell content is changed or not. Deleted neighborhood cell and base cells are selected by using test controller, writing and reading of base cell can be done by using R/W controller.](https://computerresearch.org/index.php/computer/article/download/1709/version/101260/1-FPGA-Implementation_html/22635/image-4.png)

| Year 2018 |