Artificial Intelligence formulated this projection for compatibility purposes from the original article published at Global Journals. However, this technology is currently in beta. *Therefore, kindly ignore odd layouts, missed formulae, text, tables, or figures.*

# Architecture Considerations of LTE/WCDMA Wideband Power Amplifier for Efficiency Improvement

Pinghua Chen

Received: 13 December 2018 Accepted: 4 January 2019 Published: 15 January 2019

#### 6 Abstract

3

4

14

7 An enhanced architecture for a broadband power amplifier (PA) for LTE and WCDMA

$_{\rm 8}~$  hand sets using In GaP/Ga As hetero-junction bipolar transistor (HBT) process is presented.

9 A two-stage PA solution adopting switchable driver-stage amplifier without employing input

<sup>10</sup> switch is proposed to reduce loss and help with power efficiency improvement. Furthermore, in

<sup>11</sup> order to enhance the power-added efficiency (PAE) at the low output power level, a two-chain

<sup>12</sup> amplifying structure in parallel has been implemented. For wideband 1.71-1.98GHz, the

$_{13}$  fabricated PA shows  $>\!\!27\mathrm{dB}$  of Gain and  $>\!\!38$

#### 15 Index terms—

## 16 1 Introduction

s more and more cellular communication services are developed in recent mobile terminals, the multi-mode multi-17 band power amplifiers (PAs) is required to cramp multiple bands into a single front end [1] ???] ??3]. Besides, 18 to accommodate higher data rate of the leading WCDMA and LTE signals and extend the battery life of the 19 handsets, high linearity and efficiency are as two most stringent specifications for the design of modern broadband 20 PA ??4, ??]. Generally, the cellular PA is designed to operate with significant back-off for high linearity, but 21 at the same time, this will decrease the power efficiency remarkably ???]. Therefore, various techniques have 22 23 been presented for efficiency improvement ??8] ??9] ??10] ??11]. This work, based on cost and integration considerations, introduces a novel broadband two-stage PA architecture which can minimize the degradation of 24 linearity and efficiency, and at the same time, satisfy the system gain requirement. Furthermore, a two-chain 25 parallel-amplifier structure simultaneously realized to improve the power added efficiency (PAE) while the PA 26 is operating in back-off by disabling one of the chains. 27

## 28 2 II. Circuit Architecture Considerations

structure. With this configuration, the system gain specification of 27dB is extremely easy to be achieved even though the insertion loss (IL) of the input switch is around1.5 dB while the linearity and efficiency would be degraded owing to the extra stage and dc consumption.

To improve the PA's linearity and efficiency, two-stage solution seems to be a better choice, however, it is 32 difficult to satisfy the gain requirement in wideband system when only employing two-stage PA architecture 33 with 1.5dB IL of input switch. If there is a two-stage PA solution where the input switch can be removed, 34 then it is possible to meet the gain spec for LTE/WCDMA systems. Based on this idea, we presents a two-35 stage architecture with switchable driver stage, as shown in Figure ??1 (b), the input of the first driver stage 36 37 is connected to the Band1/2 RF input pin while the input of the second one is linked to Band 4 RF input 38 pin, both outputs are connected to the input of the second power stage. Depending on the logic voltage level 39 applied to the bias circuits, one of the two switched driver stages is activated for different RF input paths. This solution can not only help with the linearity and efficiency enhancement due to the absence of additional stage, 40 but also reduce losses and improve integration as an input switch using extra GaAs pHEMT or SOI process is 41 not required anymore. Furthermore, in view of the trade-off between efficiency and linearity, a Mid-Class AB 42 operation is selected for the first stage (driver stage) of the presented PA, whereas a Deep-Class AB dc bias is set 43 for the second stage (power stage). Nonetheless, even with this arrangement, the efficiency of the PA decreases 44

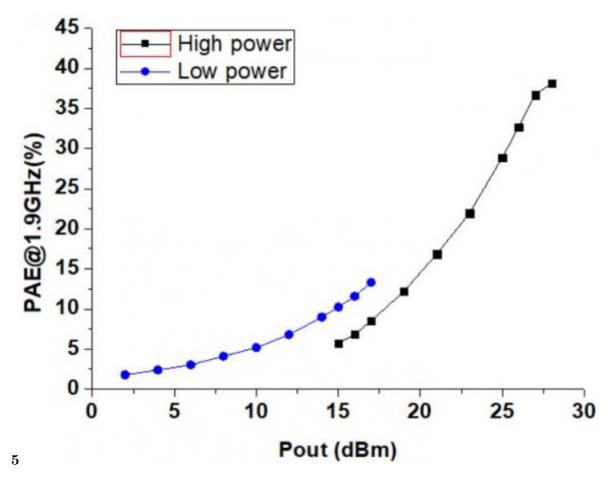

## 4 FABRICATION AND MEASUREMENT

as the input signal decreases in power. At these lower power levels, the PA's operating points are lowered further 45 away from its saturation point, which leads to severe degradation of the PAE. To achieve high efficiency over 46 a wide range of input power level, a twostage broadband PA architecture with switchable driverstage amplifier 47 adopting dual-chain strategy have been developed, as shown in Figure ?? 2. Either driver stages or power stage 48 is composed of two-chain hetero-junction bipolar transistor (HBT) amplifiers with identical emitter areas. The 49 two driver-stage amplifier chains for Band1/2 and Band4, respectively, have a same emitter area of 280?m 2 and 50  $350?\mathrm{m}\ 2$  , and the two power-stage amplifier chains have a same emitter area of  $2000?\mathrm{m}\ 2$  . In the high-power 51 mode (HPM), two-chain HBT amplifiers are activated for high output power and the PA can obtain a P1dB 52 of 28dBm, while for the low-power mode (LPM), only the main-chain amplifiers are enabled to achieve a P1dB 53 of 17dBm and the aided-chain ones are disabled to reduce the bias voltage and quiescent current, and thus 54 benefitting the efficiency improvement in the presence of low input power level. Architecture considerations of 55 LTE/WCDMA wideband power amplifier for efficiency improvement 56 In addition, at wo-section LC low-pass filter (LPF) type network is utilized for output matching to realize

In addition, at wo-section LC low-pass filter (LPF) type network is utilized for output matching to realize broadband, and a second harmonic traps are merged into the output matching network to achieve better harmonic suppression performance. Summary

## 60 **3 III.**

## <sup>61</sup> 4 Fabrication and Measurement

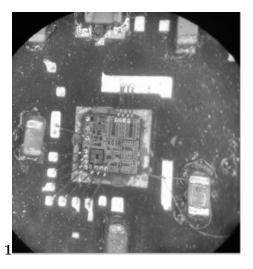

Figure 1: Figure 1. (Figure 1 :

62

1

$<sup>^{1}</sup>$ © 2019 Global Journals

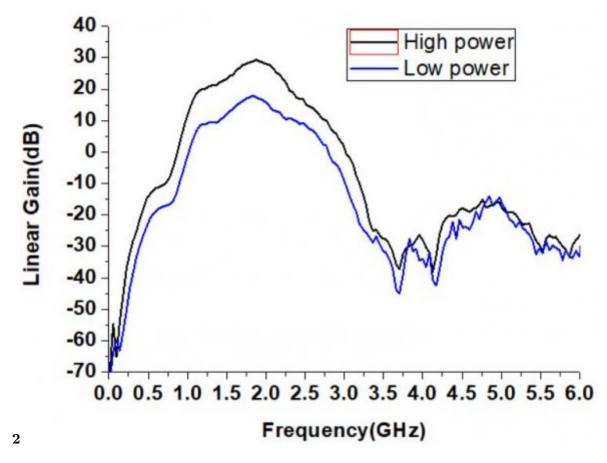

Figure 2: Figure 2 :

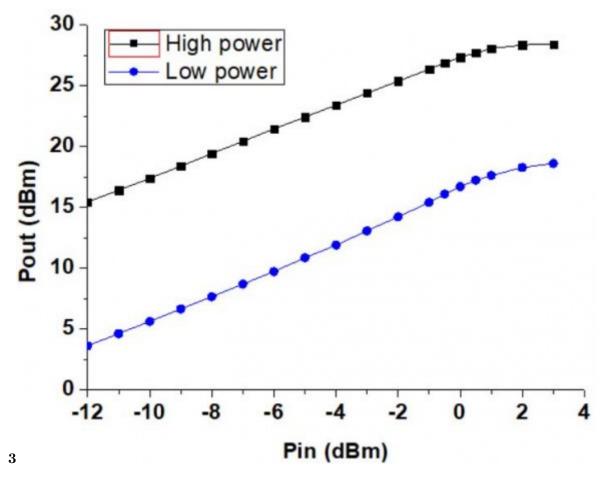

Figure 3: Figure EFigure 3 :

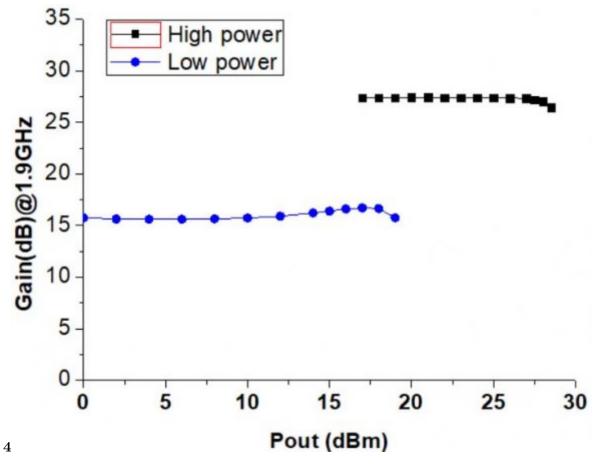

Figure 4: Figure 4 :

Figure 5: Figure 5 :

## 63 .1 Acknowledgments

<sup>64</sup> The authors wish to acknowledge all the faculty staffs in GDUT for their sincerely assistance and support to this <sup>65</sup> work.

${}_{66}\qquad {}_{Lastly,\,aquiescent\,current\,(Icq)\,of\,roughly 80 mA \,for\,HPM \,and\,20 mA for\,LPM \,have \,been \,gained \,with \,continuous-$

wave power measurement. The presented PA module reveals favorable and competitive efficiency performance in

the broadband WCDMA/LTE handset applications.

A two-stage dual-chain In GaP/Ga As HBT power amplifier module with switchable driver stages is implemented and demonstrated for multi band multi mode WCDMA and LTE handsets applications. The

<sup>71</sup> wideband PA module shows a38% of PA Eat 28dBm output power, and 13% of PAE at 17dBm output <sup>72</sup> powerat1.9GHz, which demonstrating that the presented architecture benefits the power usage efficiency

<sup>73</sup> improvement of the PA when operating in the back-off.

[Yamamoto and Miyashita] Kazuya Yamamoto , Miyo Miyashita . A WCDMA multiband power amplifier module

with Si-CMOS/GaAs-HBT hybrid power-stage configuration,